Innovation for the next generation

# ML4079

# 8-Lane 8.5-15 & 21-30 Gbps | 200G Bit Error Ratio Tester

Vertical & Horizontal Eye Closure | Bathtub Curve Measurement | Eye Contour Measurement | Receiver Sensitivity | Jitter Tolerance | Custom Pattern 40 bits

# Summary

With the accelerated growth of hyperscale datacenters, the performance demands on Ethernet network infrastructure is increasing exponentially, and customer expectations for high-speed data throughput is at an all-time high. As a result, Bit Error Rate Testers (BERT) have become a cornerstone for physical layer testing, from qualifying fiber optic and copper-wire digital data transmission lines to testing signal integrity.

A BERT generates a sequence of bits through a communication channel and the received bits are then compared against the transmitted bits. A Bit Error Ratio (BER) evaluates the full end-to-end performance of a connectivity system and assures communication reliability.

The ML4079 is a 8x30 Gbps BERT that supports NRZ signal generation required for 100 GbE measurements. It is ideally suited for the production testing of systems, components, and Electro-Optical Modules. It supports the required test patterns defined by IEEE and OIF. Other features include signal-to-noise ratio (SNR) and histogram measurements, as well as transmitter and receiver equalizers.

# **ML4079**

# 8 Channels BERT

## Introduction

The ML4079 is an eight Lane Pulse Pattern Generator and Error Detector up to 30.2 Gbps that is fully equipped for laboratory and production testing of systems, components, and Electro-Optical Modules. This instrument covers all the critical bitrates for 10, 40, 100 and 200G Ethernet, 16 and 32GFC as well as CPRI. The product has instrument-grade 2.92 mm K connectors.

## **Key Features**

#### Transmit

- Data Rates: 8.5-15 & 21-30 Gbps

- Low intrinsic jitter

- Ability to tune the bit rate in steps of 100 kbps and find the RX PLL locking margin

- Automated J2/J9 measurement

Available patterns are:

- PRBS 7/8/15/23/31 and their inverses

- Error injection

- 3-tap LUT-based Pre- and Post-emphasis

#### Receive

- Programmable front-end attenuator

- Error-detection on following patterns:

PRBS 7/9/15/16/23/31

- Automatic pattern detects

- LOS indicators.

## **Target Applications**

- Interconnect testing QSFP-DD, OSFP

- Backplane testing

- Interference and crosstalk testing

- Receiver sensitivity testing

- Electro-Optical module testing

- Electrical eye testing for 200 Gbps Ethernet,

- MLD/CAUI application, OIF CEI-28G-VSR, CPPI4, CAUI-4, GAUI-8, 32G Fiber Channel chip to module.

#### **ML BERT GUI**

- Tests 8-channel BER test at the same time

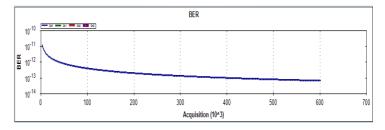

- Supports BER curve

- Provides multiple and single layouts of bathtub and eye contour

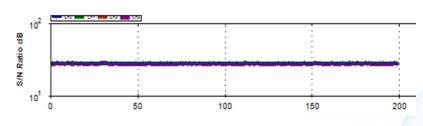

Figure 2: S/N Ratio over 200 captures

# **Specifications**

| Parameter                         | Specifications                                                   |  |

|-----------------------------------|------------------------------------------------------------------|--|

| Bit Rates                         | 8.5-15 and 21-30 Gbps                                            |  |

| Data Format                       | NRZ                                                              |  |

| Dattorn                           | PRBS 7, 9, 15, 23, 31, and User Defined Pattern 16 bits at 10G & |  |

| Pattern                           | 40 bits at 25G                                                   |  |

| TX Amplitude Differential         | 200-800 mV                                                       |  |

| TX Amplitude Adjustment           | 200 mV/step                                                      |  |

| Pre-Emphasis                      | 6 dB                                                             |  |

| Pre-Emphasis Resolution           | 20 steps                                                         |  |

| Equalizing Filter Spacing         | -                                                                |  |

| Total Jitter pk-pk @10G           | 10 ps (typical)                                                  |  |

| Total Jitter pk-pk @25G           | 12 ps (typical)                                                  |  |

| Rise/Fall Time (20-80%) @25G      | 17 ps                                                            |  |

| Sinusoidal Phase Modulation       | -                                                                |  |

| Sinusoidal Jitter Frequency       | -                                                                |  |

| Random Jitter in Phase Modulation | -                                                                |  |

| Output Return Loss up to 10GHz    | < -15 dB                                                         |  |

| Output Return Loss (16-25GHz)     | < -8 dB                                                          |  |

| TX Skew Control Range             | -                                                                |  |

| Lane to Lane Skew Resolution      | -                                                                |  |

| Error Detector Input Amplitude    | 110-1050 mVpp at 11G, 1200 mVpp at 25G                           |  |

| Error Detector Maximum Input      | 1200 mV Diff                                                     |  |

| Error Detector Input Sensitivity  | 30 mVpp at 10.3125G / 50 mVpp at 28G                             |  |

| Phase Scan Resolution             | 7 bits                                                           |  |

| Vertical Scan Resolution          | 8 bits                                                           |  |

| Input CTLE Dynamic Range          | 10 dB                                                            |  |

| Reference Clock Output            | Rate/32 for 8.5-15G and Rate/80 for 21-30G                       |  |

| Reference Clock Output Amplitude  | 550-850 mVpp                                                     |  |

| Reference Clock Input             | Rate/32 for 8.5-15G and Rate/80 for 21-30G                       |  |

| Reference Clock Input Amplitude   | 300-1900 mVpp                                                    |  |

| Clock Data Recovery               | Rate/N (user selectable from 8 and 16)                           |  |

| Power Requirement                 | 12 V dc, 40 W max                                                |  |

\*Output amplitude setting error: ±30 mV

$^{\rm 1}$  With appropriate de-emphasis and short cables; measured on a scope with >40 GHz analog BW  $^{\rm 2}$  Rev A3

### **Mechanical Dimensions**

The ML4079 is a benchtop instrument that fits in a 19-inch 2U rack. MultiLane also supplies the needed brackets.

## **Ordering Information**

| Option | Description                                      |  |

|--------|--------------------------------------------------|--|

| ML4079 | 200G BERT (8 CH 21-30 GBd NRZ)                   |  |

| 3YW    | Total 3-year warranty                            |  |

| CAL    | Single calibration                               |  |

| 3YWC   | Total 3-year warranty with 3 annual calibrations |  |

## **Recommended Accessories**

| Instruments | Recommended<br>Phase matched cable pairs | Alternative<br>Phase matched cable sets | Comments                                |

|-------------|------------------------------------------|-----------------------------------------|-----------------------------------------|

| ML4079      | 16x MLCBPM-2.92-30                       | 2x MLCBPM-2.92-30-16                    | 2.92 mm connector 2x16 channel 30 cm    |

| ML4079      | 16x MLCBPM-2.92-60                       | 2x MLCBPM-2.92-60-16                    | 2.92 mm connector 2x16 channel<br>60 cm |

Please contact us at <a href="mailto:sales@multilaneinc.com">sales@multilaneinc.com</a>.